次世代を担う高性能なコンピュータシステムを創り出す

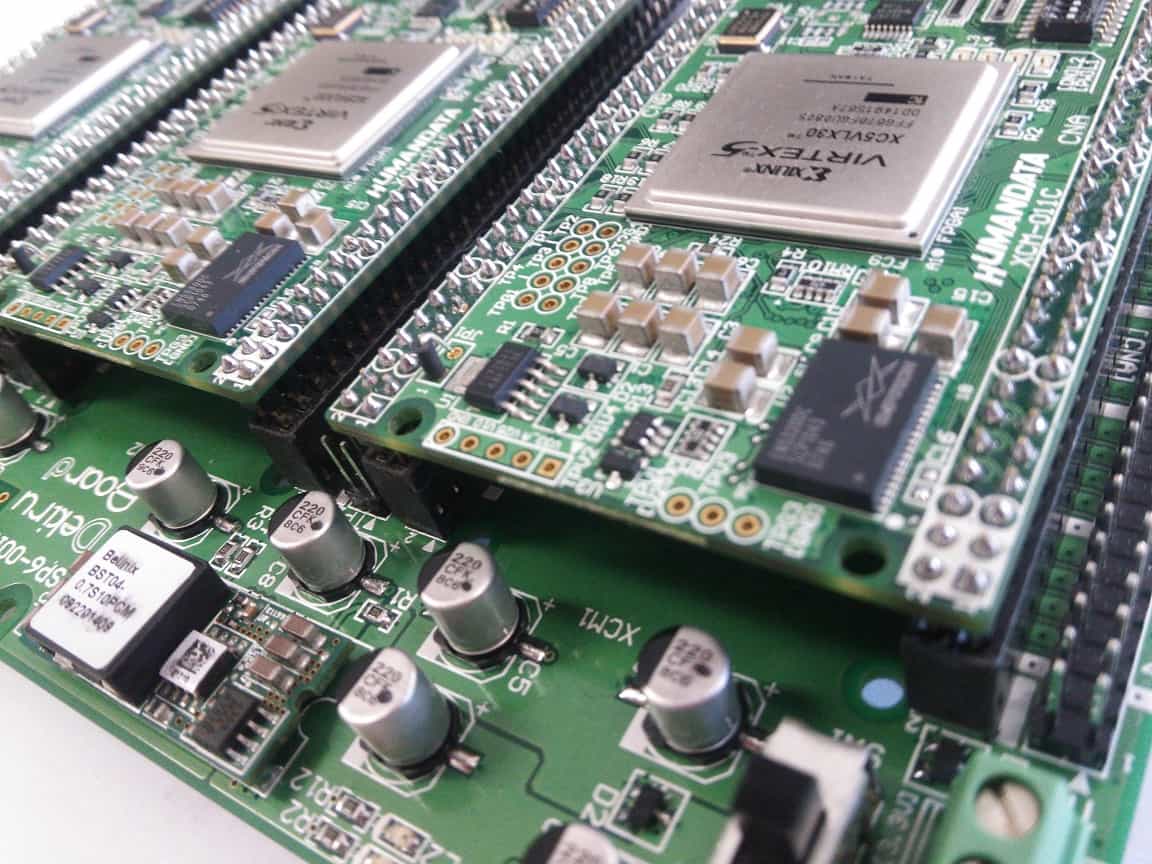

現在,大多数のデジタルシステムはクロックパルスに同期して動作しています.しかし,高速なクロックパルスは,消費電力が増大するだけでなくシステムの動作が不安定となる要因となります.そこで本研究室では,クロックパルスを用いない非同期式回路に基づいて,大規模デジタルシステムや生体信号処理用プロセッサの高性能化・低消費電力化に関する研究を行っています.また,これらの設計と実装には再構成型集積回路(FPGA)を用いており,監視カメラシステムや医用画像診断システム等を対象とした画像処理のハードウェア化にも取り組んでいます.

PAGE

PAGE